kopia lustrzana https://github.com/cariboulabs/cariboulite

Update README.md

rodzic

9206d5b2d5

commit

c447d2d27b

44

README.md

44

README.md

|

|

@ -1,20 +1,37 @@

|

|||

# CaribouLite

|

||||

CaribouLite is an affordable, open-source SDR platform that is also a certified HAT for the Raspberry-Pi family of boards (40-pin versions only). It is built for makers, hackers, and researchers and was designed to complement the SDR current eco-systems offering with a scalable, standalone dual-channel software-defined radio.

|

||||

CaribouLite is an affordable, educational, open-source SDR platform that is also a HAT for the Raspberry-Pi family of boards (40-pin versions only). It is built for makers, hackers, and researchers and was designed to complement the SDR current eco-systems offering with a scalable, standalone dual-channel software-defined radio.

|

||||

|

||||

<table>

|

||||

<tr>

|

||||

<td><img src="https://user-images.githubusercontent.com/616259/113452512-ce80d480-940c-11eb-93c7-d980459d7637.png" alt="Top View" height="200"></td>

|

||||

<td><img src="https://github.com/cariboulabs/cariboulite/blob/main/hardware/rev1/side.png" alt="Top View" height="300"></td>

|

||||

</tr>

|

||||

<tr>

|

||||

<td>Top view</td>

|

||||

<td>Top view, Prototype Rev1</td>

|

||||

</tr>

|

||||

</table>

|

||||

|

||||

Unlike many other HAT projects, CaribouLite utilizes the <B>SMI</B> (Secondary Memory Interface) present on all the 40-pin RPI versions. This interface is scarcely documented by both Raspberry-Pi documentation and Broadcomm's reference manuals. An amazing work done by https://iosoft.blog/2020/07/16/raspberry-pi-smi/ (code in https://github.com/jbentham/rpi) in hacking this interface contributes to CaribouLite's technical feasibility. The SMI interface should allows exchanging ~500+ Mbit/s between the RPI and the HAT, and yet, the results vary between the different versions of RPI. The results further depends on the specific RPI version's DMA speeds.

|

||||

Unlike many other HAT projects, CaribouLite utilizes the <B>SMI</B> (Secondary Memory Interface) present on all the 40-pin RPI versions. This interface is not thoroughly documented by both Raspberry-Pi documentation and Broadcomm's reference manuals. An amazing work done by [https://iosoft.blog/2020/07/16/raspberry-pi-smi/] (code in [https://github.com/jbentham/rpi]) in hacking this interface contributes to CaribouLite's technical feasibility. A deeper overview of the interface is provided in [https://github.com/cariboulabs/cariboulite/blob/main/docs/Secondary%20Memory%20Interface.pdf]. The SMI interface allows exchanging >500Mbit/s between the RPI and the HAT, and yet, the results vary between the different versions of RPI. The results further depends on the specific RPI version's DMA speeds.

|

||||

|

||||

In our application, each ADC sample contains 13 bit (I) and 13 bit (Q), that are streamed with a maximal sample rate of 4 MSPS from the AT86RF215 IC. Such channel requires 4 bytes (samples padded to 32-bit) per sample (and I/Q pair) => 16 MBytes/sec which are 128 MBits/sec. By packing the samples into 24 bit I/Q pair (converting to 12-bit samples by decimating the samples), this required throughput decreases to 96 Mbit/sec. The AT86RF215 IC from Microchip contains two RX I/Q outputs from its ADCs (one for each physical channel - sub-1GHz and 2.4GHz), and a single TX I/Q intput directed to the DACs.

|

||||

In our application, each ADC sample contains 13 bit (I) and 13 bit (Q), that are streamed with a maximal sample rate of 4 MSPS from the AT86RF215 IC. This channel requires 4 bytes (samples padded to 32-bit) per sample (and I/Q pair) => 16 MBytes/sec which are 128 MBits/sec. In addition to the 13 bit for each of I/Q, the Tx/Rx streams of data contain flow control and configuration bits. The modem (AT86RF215) IC by Microchip contains two RX I/Q outputs from its ADCs (one for each physical channel - sub-1GHz and 2.4GHz), and a single TX I/Q intput directed to the DACs.

|

||||

|

||||

Deeper project details can be found in our Wiki pages - https://github.com/babelbees/CaribouLite/wiki

|

||||

**A working prototype version** of the board has been produced and tested to meet product requirements. In a meanwhile, a second revision of the board is being produced with the following main updates (see picture below):

|

||||

1. Image rejection filtering improvement - U10 and U12 (HPF & LPF) - have been replaced by integrated LTCC filters by MiniCircuits

|

||||

2. Removing FPGA flash - redundant given the fact that the the RPI configures the FPGA in <1sec over SPI.

|

||||

3. Board layout improvements and overlays (silkscreen) beautification (including logo)

|

||||

4. More detailed changes in the schematics.

|

||||

|

||||

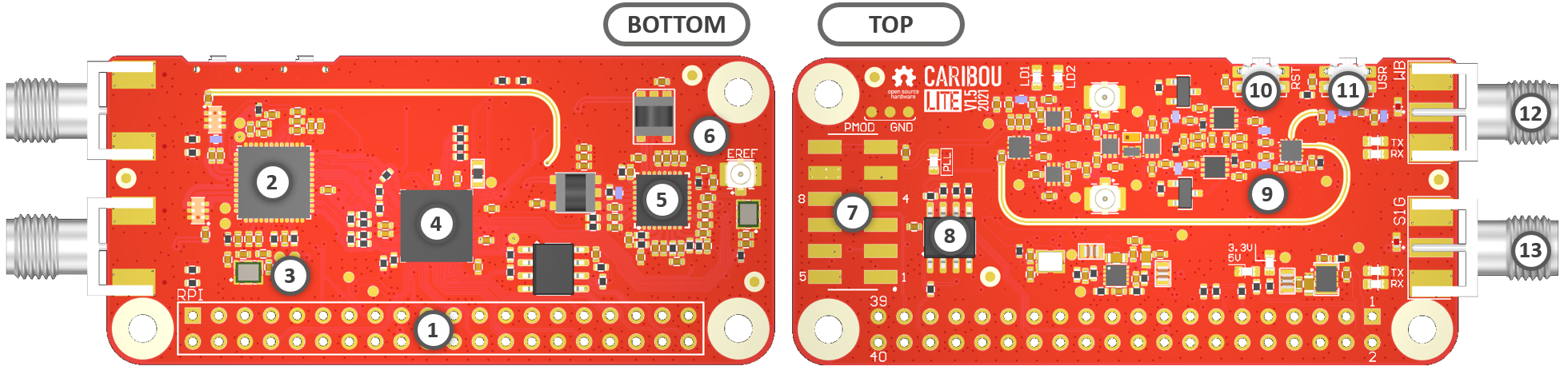

In CaribouLite-R2 the PCB design has been thoroughly re-thought to meet its educational needs. The RF path has been annotated with icons to ease the orientation in the schematics sheets, friendly silk writing was added describing system's components by their functionality rather than logical descriptors, and more.

|

||||

|

||||

<table>

|

||||

<tr>

|

||||

<td><img src="https://github.com/cariboulabs/cariboulite/blob/main/hardware/rev2/pictures/cad_image.png" alt="Top View" height="500"></td>

|

||||

</tr>

|

||||

<tr>

|

||||

<td>Top & Bottom view, Production Rev2</td>

|

||||

</tr>

|

||||

</table>

|

||||

|

||||

**Deeper project details will be published shortly in our Wiki pages.**

|

||||

|

||||

# Specifications

|

||||

|

||||

|

|

@ -24,13 +41,13 @@ Deeper project details can be found in our Wiki pages - https://github.com/babel

|

|||

|

||||

<table>

|

||||

<tr>

|

||||

<td><img src="https://user-images.githubusercontent.com/616259/113505667-03924180-9549-11eb-8ced-69ead48a2357.png" alt="spectra"></td>

|

||||

<td><img src="https://github.com/cariboulabs/cariboulite/blob/main/hardware/rev1/frequencies.png" alt="spectra"></td>

|

||||

</tr>

|

||||

<tr>

|

||||

<td style="text-align:center">Applicable spectra, S1G - sub-1GHz, WB - Wide tuning channel</td>

|

||||

</tr>

|

||||

</table>

|

||||

<B>Note</B>: The gaps are defined by the design constarints of the system and may not exist in real-life hardware.

|

||||

<B>Note</B>: The gaps are defined by the design constarints of the system and may not exist in real-life hardware. Actual modem synthisizer outputs test show wider margins ar room temperature than those written in the datatsheet, but, as noted by Microchip, performance may suffer.

|

||||

|

||||

|

||||

<B>FPGA specifications:</B>

|

||||

|

|

@ -41,13 +58,6 @@ Deeper project details can be found in our Wiki pages - https://github.com/babel

|

|||

|

||||

<B>Applicable RPI models</B>: RPI_1(B+/A+), RPI_2B, RPI_Zero(Zero/W/WH), RPI_3(B/A+/B+), RPI_4B

|

||||

|

||||

<B>Prices @ 2500 units:</B>

|

||||

- Total: <$38.5

|

||||

- BOM: ~$35

|

||||

- PCB: <$1

|

||||

- PCBA: <$2.5

|

||||

|

||||

|

||||

Parameter | Sub-1GHz | Wide Tuning Channel

|

||||

---------------------------|------------------------------|------------------------------------------------------------------

|

||||

Frequency tuner range | 389.5-510 MHz / 779-1020 MHz | 30 MHz - 6 GHz (excluding 2398.5-2400 MHz and 2483.5-2485 MHz)

|

||||

|

|

@ -57,7 +67,7 @@ Max Transmit power | 14.5 dBm | >14 dBm @ 30-2400 MH

|

|||

Receive noise figure | <4.5 dB | <4.5 dB @ 30-3500 MHz, <8 dB @ 3500-6000 MHz

|

||||

|

||||

# Board Layout

|

||||

|

||||

|

||||

|

||||

<B>Description:</B>

|

||||

1. Rasperry-Pi 40-pin connector

|

||||

|

|

@ -73,5 +83,3 @@ Receive noise figure | <4.5 dB | <4.5 dB @ 30-3500 MH

|

|||

11. User custom switch + RPI HAT EEPROM reconfiguration (write-enable) switch

|

||||

12. Wide band SMA connector

|

||||

13. Sub 1-GHz SMA connector

|

||||

|

||||

|

||||

|

|

|

|||

Ładowanie…

Reference in New Issue